# MOS INTEGRATED CIRCUIT $\mu$ PD72042B

# LSI DEVICE FOR Inter Equipment Bus<sup>™</sup> (IEBus<sup>™</sup>) PROTOCOL CONTROL

The  $\mu$ PD72042B is a microcomputer peripheral LSI device for IEBus protocol control.

The  $\mu$ PD72042B performs all the processing required for layers 1 and 2 of the IEBus. The device incorporates large transmission and reception buffers, allowing the microcomputer to perform IEBus operations without interruption. It also contains an IEBus driver and receiver, allowing it to directly connected to the bus.

# FEATURES

JEC

$\odot$  Control of layers 1 and 2 of the IEBus protocol

- Support of a multi-master scheme

- Broadcast function

- Two communication modes having different transmission speeds can be selected.

|        | When operating<br>at 6 MHz | When operating<br>at 6.29 MHz |

|--------|----------------------------|-------------------------------|

| Mode 0 | Approx. 3.9 Kbps           | Approx. 4.1 Kbps              |

| Mode 1 | Approx. 17 Kbps            | Approx. 18 Kbps               |

○ Built-in IEBus driver and receiver

- Transmission and reception buffers

- Transmission buffer: 33 bytes, FIFOReception buffer: 40 bytes, FIFO (capable of<br/>holding more than one frame<br/>of reception data.)

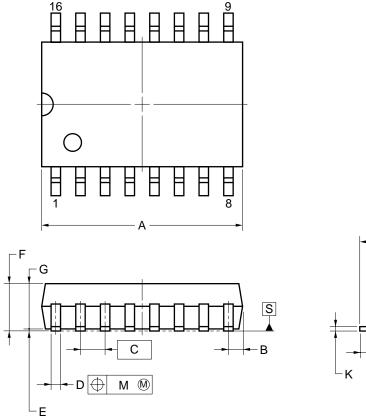

# **\*** ORDERING INFORMATION

| Part number      | Package                            |

|------------------|------------------------------------|

| $\mu$ PD72042BGT | 16-pin plastic SOP (9.53 mm (375)) |

○ Microcomputer interface

Three-/two-wire serial I/O

- Transfer starting with LSB

- Program crashes can be detected by means of a watchdog timer.

- $\odot$  Low power consumption (standby mode): 50  $\mu$ A (max)

- Oscillator frequency (fx): 6 MHz, 6.29 MHz

- frequency accuracy: ±1.5%

- $\odot$  Operating voltage: 5 V ±10%

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

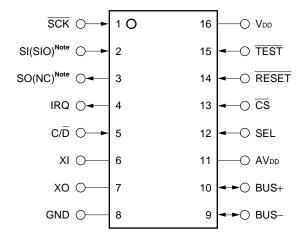

# **PIN CONFIGURATION (TOP VIEW)**

• 16-pin plastic SOP (9.53 mm (375)) μPD72042BGT

**Note** Parentheses indicate the state corresponding to two-wire serial I/O mode.

| AVDD       | : Main power supply for IEBus (connected to the $V_{DD}$ pin) |

|------------|---------------------------------------------------------------|

| BUS–, BUS+ | : IEBus I/O                                                   |

| C/D        | : Command/data switch input                                   |

| CS         | : Chip select input                                           |

| GND        | : Ground                                                      |

| IRQ        | : Interrupt request output                                    |

| NC         | : No connection                                               |

| RESET      | : Reset input                                                 |

| SCK        | : Serial clock input                                          |

| SEL        | : Serial mode selection                                       |

| SI         | : Serial data input                                           |

| SIO        | : Serial data I/O                                             |

| SO         | : Serial data output                                          |

| TEST       | : Test input (connected to the VDD pin)                       |

| Vdd        | : Main power supply                                           |

| XI, XO     | : System clock                                                |

|            |                                                               |

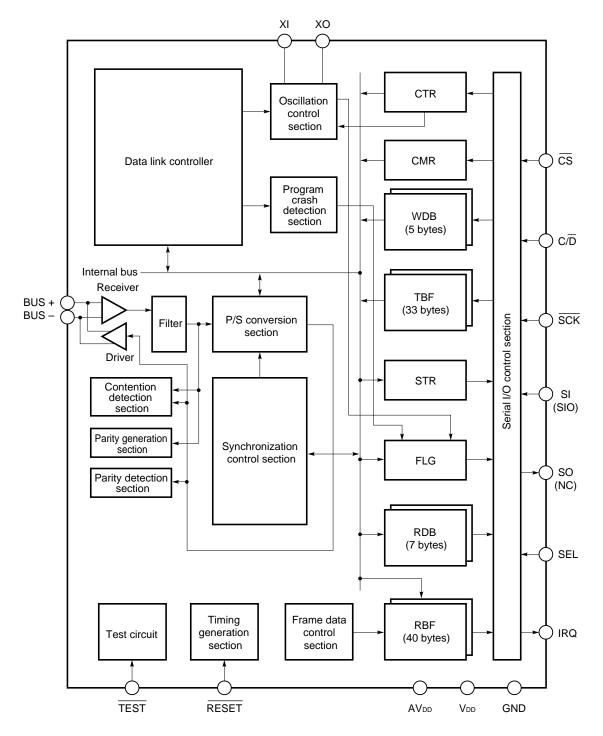

# **BLOCK DIAGRAM**

Remark The pin names in parentheses are used when two-wire serial I/O is selected.

# CONTENTS

| 1. | PIN | FUNCTIONS                                        | 6  |

|----|-----|--------------------------------------------------|----|

|    | 1.1 | PIN FUNCTIONS                                    | 6  |

| 2. | IEB | us OPERATION                                     | 8  |

|    | 2.1 | OVERVIEW                                         |    |

|    | 2.2 | IEBus COMMUNICATION PROTOCOL                     |    |

|    |     | 2.2.1 Bus Mastership Determination (Arbitration) |    |

|    |     | 2.2.2 Communication Mode                         |    |

|    |     | 2.2.3 Communication Address                      | 11 |

|    |     | 2.2.4 Broadcast                                  | 11 |

|    | 2.3 | TRANSMISSION PROTOCOL                            | 11 |

|    | 2.4 | TRANSMISSION DATA (CONTENTS OF THE DATA FIELD)   | 17 |

|    | 2.5 | BIT FORMAT                                       | 21 |

| _  |     |                                                  |    |

| 3. | -   |                                                  |    |

|    | 3.1 |                                                  |    |

|    | 3.2 | DATA TRANSFER FORMAT                             |    |

|    |     | 3.2.1 Three-Wire Data Transfer (SEL = 1)         |    |

|    |     | 3.2.2 Two-Wire Data Transfer (SEL = 0)           |    |

|    | 3.3 |                                                  |    |

|    | 3.4 | STANDBY MODE SETTING AND CANCELLATION            |    |

|    | 3.5 | RESET MODE SETTING AND CANCELLATION              | 28 |

| 4. | REC | GISTERS                                          | 29 |

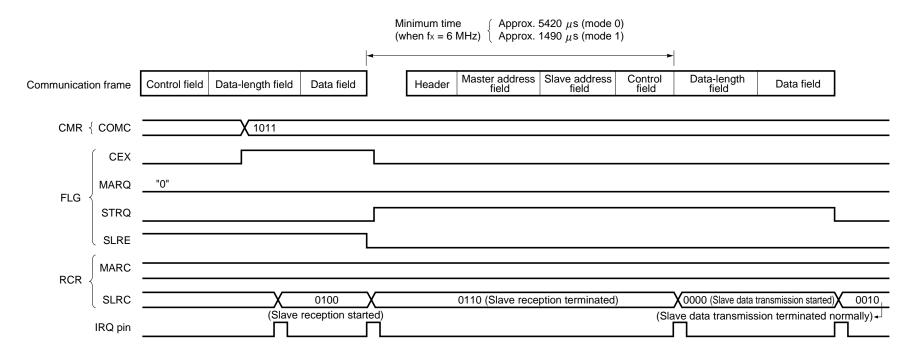

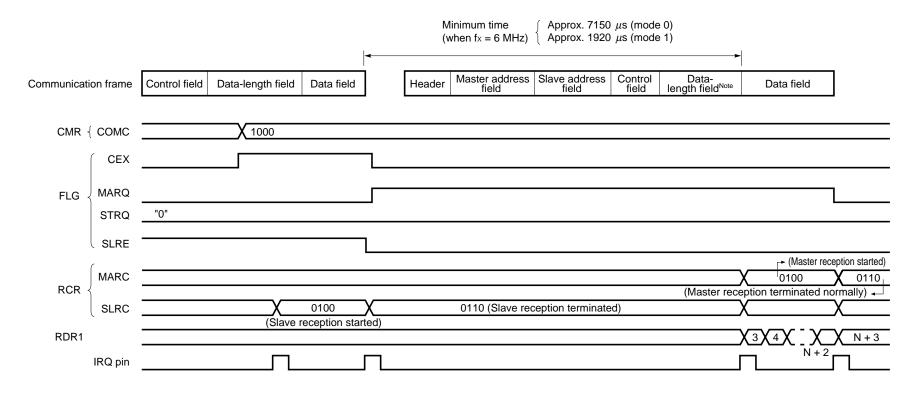

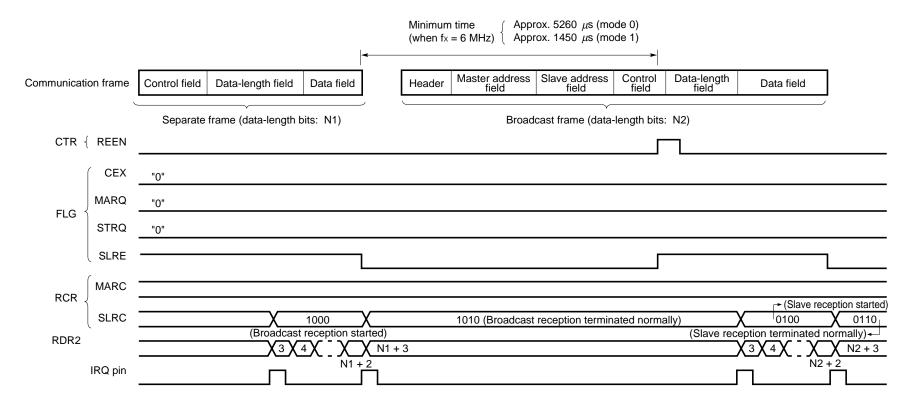

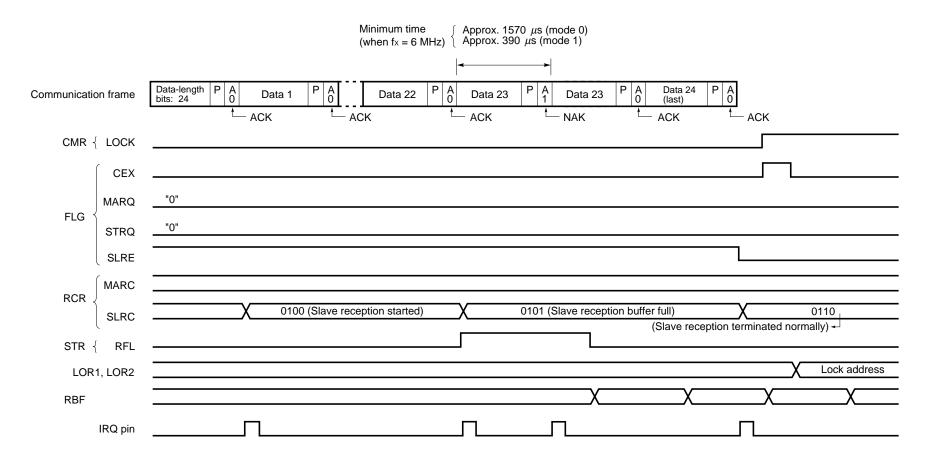

| 5. | EXA | MPLE TIMINGS FOR COMMUNICATION                   | 59 |

| 6. | EXA | MPLE MICROCOMPUTER PROCESSING FLOW               | 67 |

|    | 6.1 | COMMUNICATION FLAGS                              | 68 |

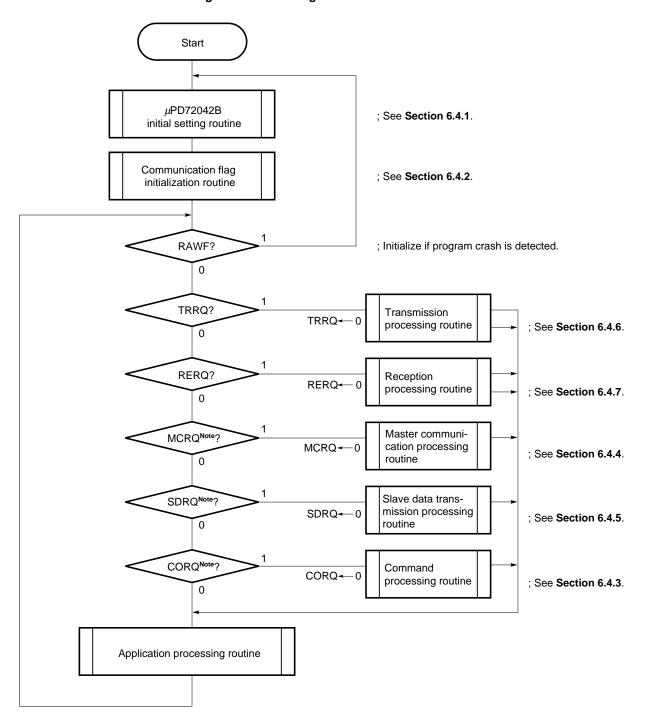

|    | 6.2 | MAIN ROUTINE                                     | 69 |

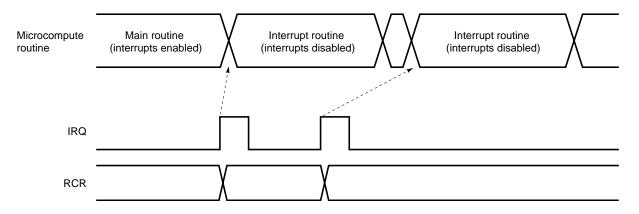

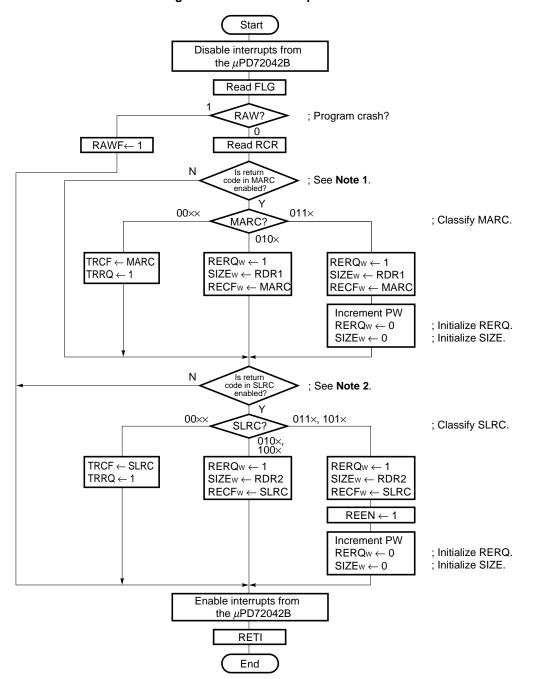

|    | 6.3 | INTERRUPT ROUTINE                                | 70 |

|    | 6.4 | PROCESSING ROUTINES                              |    |

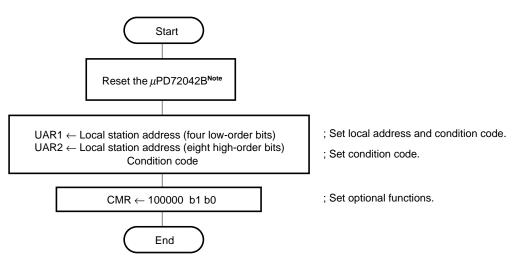

|    |     | 6.4.1 μPD72042B Initial Setting Routine          |    |

|    |     | 6.4.2 Communication Flag Initialization Routine  |    |

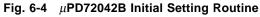

|    |     | 6.4.3 Command Processing Routine                 |    |

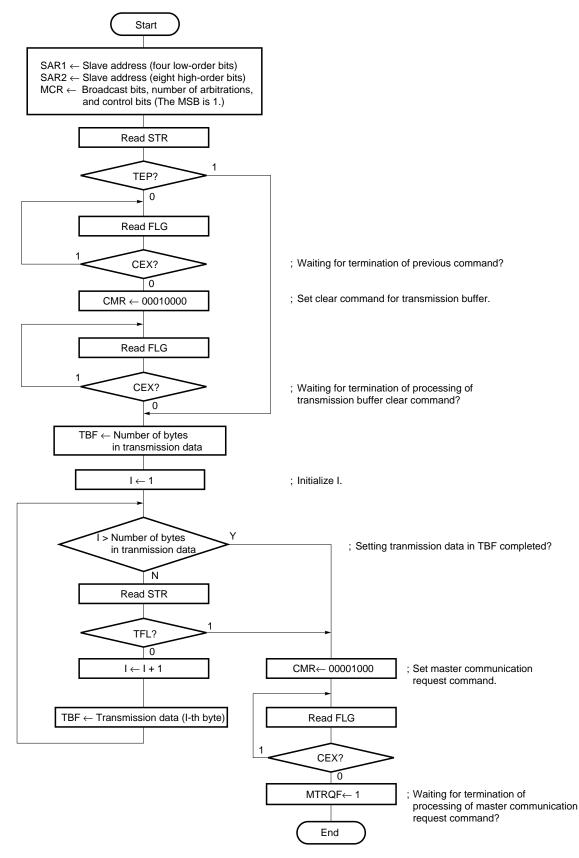

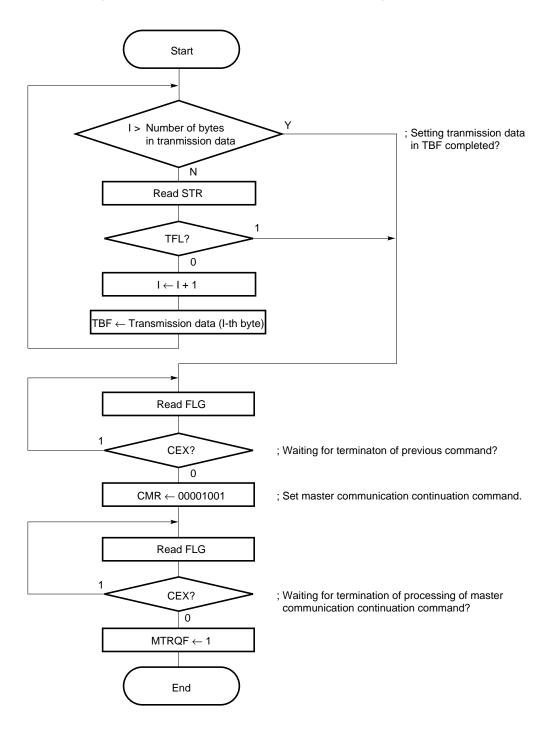

|    |     | 6.4.4 Master Communication Processing Routine    |    |

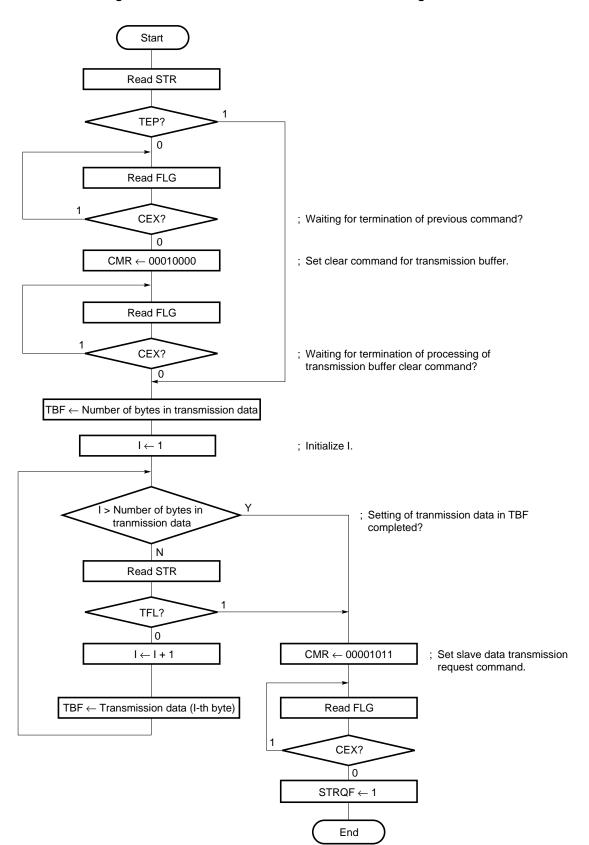

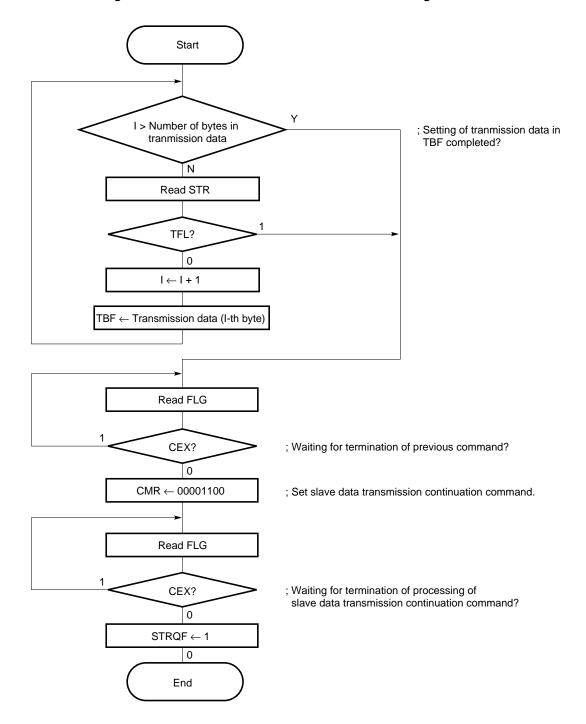

|    |     | 6.4.5 Slave Data Transmission Processing Routine |    |

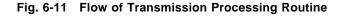

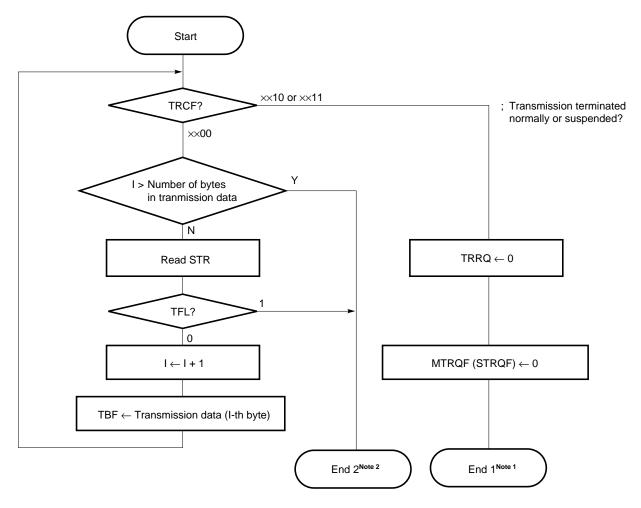

|    |     | 6.4.6 Transmission Processing Routine            | 80 |

|    |     | 6.4.7 Reception Processing Routine               | 81 |

| 7. | ELE | CTRICAL CHARACTERISTICS                          | 82 |

| 8. | PAC | KAGE DRAWING                                     |    |

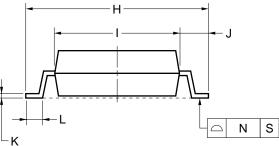

| 9. RECOMMENDED SOLDERING CONDITIONS                                                  | 87 |

|--------------------------------------------------------------------------------------|----|

| APPENDIX A MAIN DIFFERENCES BETWEEN $\mu$ PD72042A, $\mu$ PD72042B, AND $\mu$ PD6708 | 88 |

| APPENDIX B IEBus PROTOCOL ANALYZER                                                   | 88 |

# 1. PIN FUNCTIONS

# 1.1 PIN FUNCTIONS

| Pin No. | Pin <sup>Note</sup> | I/⊖Note          | Function                                                                                                                                                                                                                               | I/O format <sup>Note</sup> | When reset<br>[for both hardware<br>and software]                                                                                             |  |  |  |

|---------|---------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | SCK                 | Input            | Serial clock input pin for CPU interface                                                                                                                                                                                               | CMOS input                 | Input                                                                                                                                         |  |  |  |

| 2       | SI (SIO)            | Input (I/O)      | Serial data pin for CPU interface. (This pin<br>functions as an input pin when 3-wire serial<br>I/O mode is selected, or as an I/O pin when<br>2-wire serial I/O mode is selected.)                                                    | CMOS input<br>(CMOS I/O)   | Input                                                                                                                                         |  |  |  |

| 3       | SO (NC)             | Output<br>(none) | Serial data output pin for CPU interface. (The<br>pin functions as an output when 3-wire serial I/O<br>mode is selected. When 2-wire serial I/O mode<br>is selected, the pin is left open.)                                            | CMOS output<br>(none)      | High-impedance                                                                                                                                |  |  |  |

| 4       | IRQ                 | Output           | Output pin for making an interrupt request to the CPU. When a return code or a program crash is detected, a high-level signal is output on this pin for at least 8 $\mu$ s.                                                            | CMOS output                | Low level                                                                                                                                     |  |  |  |

| 5       | C/D                 | Input            | Input pin used to select control mode or data<br>read/write mode. When this pin is driven high,<br>internal register address setting and data read/<br>write are enabled. When the mode changes, the<br>serial clock counter is reset. | CMOS input                 | Input                                                                                                                                         |  |  |  |

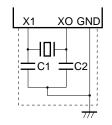

| 6<br>7  | XI<br>XO            | _                | Pins for connecting a system clock resonator. A 6- or 6.29-MHz crystal or ceramic resonator must be used. The accuracy of the frequency is as follows;<br>Mode 0, 1: $\pm 1.5\%$                                                       | _                          | When reset by<br>hardware (Oscil-<br>lation stopped)<br>XI = GND<br>XO = High level<br>When reset by<br>software (Oscil-<br>lation continued) |  |  |  |

| 8       | GND                 | _                | Ground pin                                                                                                                                                                                                                             | _                          | -                                                                                                                                             |  |  |  |

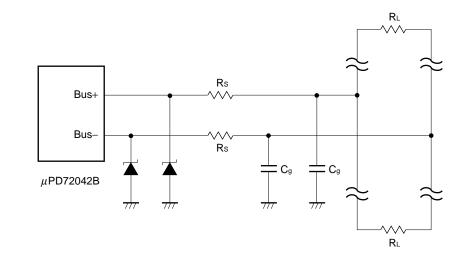

| 9<br>10 | BUS-<br>BUS+        | I/O              | I/O pins connected to the IEBus bus                                                                                                                                                                                                    | _                          | High-impedance                                                                                                                                |  |  |  |

| 11      | AVDD                | _                | Main power supply pin for the IEBus bus driver/<br>receiver. When used, this pin must be tied to<br>VDD.                                                                                                                               | -                          | _                                                                                                                                             |  |  |  |

| 12      | SEL                 | Input            | Input pin used to select either 3- or 2-wire serial I/O mode. A high-level signal on this pin selects 3-wire serial I/O mode. A low-level signal on this pin selects 2-wire serial I/O mode.                                           | CMOS input                 | Input                                                                                                                                         |  |  |  |

| 13      | CS                  | Input            | Chip select pin. When this pin is driven low, the serial interface is enabled. When this pin is driven high, the SO pin becomes high-impedance, and the serial clock counter is reset.                                                 | CMOS input                 | Input                                                                                                                                         |  |  |  |

**Note** Parentheses indicate the state corresponding to two-wire serial I/O mode.

| Pin No. | Pin   | I/O   | Function                                                                                                                                                                                               | I/O format | When reset<br>[for both hardware<br>and software] |

|---------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------|

| 14      | RESET | Input | Serial reset signal input pin. A low input causes<br>a reset. Whenever the power is turned on, a<br>low-level signal must be applied to this pin.<br>During normal operation, a high level is applied. | CMOS input | Input                                             |

| 15      | TEST  | Input | IC test pin. When used, this pin must be tied to the $V_{DD}$ pin directly.                                                                                                                            | CMOS input | -                                                 |

| 16      | Vdd   | _     | Main power supply input pin                                                                                                                                                                            | -          | -                                                 |

# 2. IEBus OPERATION

#### 2.1 OVERVIEW

The  $\mu$ PD72042B is a CMOS LSI device for the IEBus interface.

The IEBus is designed to enable the data transmission between devices in a small-scale digital data transmission system.

The  $\mu$ PD72042B is connected to a microcomputer built into a device. A serial interface (SCK, SO, and SI pins) is used for connection. The host controller (microcomputer) sets the commands and data needed for data transmission via this serial interface.

When data is transmitted, the host controller sets the data in the  $\mu$ PD72042B via the serial interface. Then, signals are output on the BUS pins (BUS+, BUS–). When data is received from the BUS pins, the host controller can read it via the serial interface.

# 2.2 IEBus COMMUNICATION PROTOCOL

The IEBus is outlined below.

- Communication method: Half duplex asynchronous communication

- Multi-master method All units connected to the IEBus can transmit data to every other connected unit.

- Broadcast function (one-unit-to-multiple-units communication)

Group broadcast : Broadcast to a specific group of units

General broadcast : Broadcast to all units

- Two modes, each offering different transmission speeds, can be selected.

|        | fx = 6 MHz       | fx = 6.29 MHz    | Maximum number of bytes transmitted (bytes/frame) |

|--------|------------------|------------------|---------------------------------------------------|

| Mode 0 | Approx. 3.9 Kbps | Approx. 4.1 Kbps | 16                                                |

| Mode 1 | Approx. 17 Kbps  | Approx. 18 Kbps  | 32                                                |

Access control: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Bus mastership priority is as follows:

Broadcast takes priority over ordinary communication (one-unit-to-one-unit communication).

Units having lower master addresses have a higher priority.

| <ul> <li>Communication scale</li> </ul> |                                                                                                                              |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Number of units                         | : 50 max                                                                                                                     |

| Cable length                            | : 150 m max (when twisted-pair cable is used <resistance 0.1="" <math="" display="inline">\Omega/m or less&gt;)</resistance> |

| Load capacity                           | : 8000 pF max <between and="" bus+="" bus-="">, fx = 6 MHz</between>                                                         |

|                                         | 7100 pF max <between and="" bus+="" bus-="">, fx = 6.29 MHz</between>                                                        |

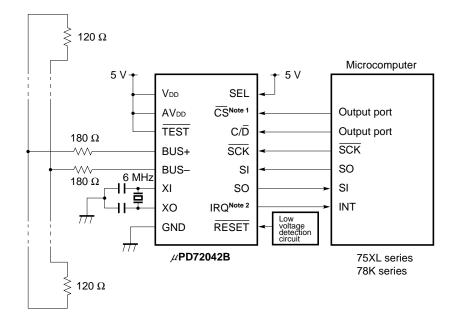

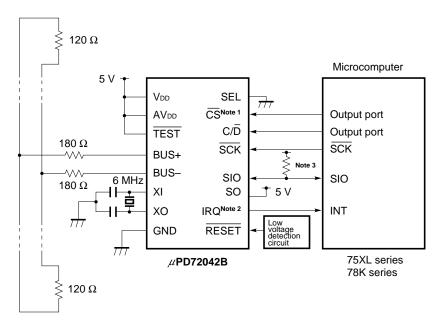

| Terminating resistance                  | : 120 Ω                                                                                                                      |

# Caution For the $\mu$ PD72042B, as a protective resistance, connect a 180- $\Omega$ resistor in series with the BUSand BUS+ pins.

## 2.2.1 Bus Mastership Determination (Arbitration)

Before devices connected to the IEBus can control other devices, they must first acquire the bus. This operation is called arbitration.

When more than one unit starts transmission at the same time, arbitration determines which of those units is allowed to use the bus.

When arbitration results in only one device being granted bus mastership, the following bus mastership priority conditions are used:

**Remark** Those devices that are defeated in arbitration can automatically enter retransmission mode. (For the  $\mu$ PD72042B, the number of retransmissions can be set by specifying a value between 0 and 7 in the MCR register.)

#### (1) Priority by communication type

Broadcast (one-unit-to-multiple-units communication) takes priority over ordinary communication (one-unit-toone-unit communication).

#### (2) Priority by master address

If the communication type is the same, the smallest master address value has the highest priority.

**Example** Each master address consists of 12 bits. A unit having master address 000H has the highest priority, while a unit having master address FFFH has the lowest priority.

#### 2.2.2 Communication Mode

The IEBus supports two communication modes, each having a different transmission speed. Table 2-1 lists the transmission speed for each communication mode and the maximum number of bytes transmitted within one communication frame.

| Table 2-1 | Transmission Speed and Maximum Number of Transmission |

|-----------|-------------------------------------------------------|

|           | Bytes in Each Communication Mode                      |

|                                        | Maximum number of transmission | Effective transmissio           | n speed <sup>Note 1</sup> (Kbps) |

|----------------------------------------|--------------------------------|---------------------------------|----------------------------------|

| Communication mode bytes (bytes/frame) | fx = 6 MHz <sup>Note 2</sup>   | fx = 6.29 MHz <sup>Note 2</sup> |                                  |

| 0                                      | 16                             | Approx. 3.9                     | Approx. 4.1                      |

| 1                                      | 32                             | Approx. 17                      | Approx. 18                       |

Notes 1. Effective transmission speed at which the maximum transfer rate is achieved

- **2.** Oscillator frequencies for the  $\mu$ PD72042B

- Cautions 1. Before devices connected to the IEBus can perform communication, an appropriate communication mode must be set. Note that if a master unit and an associated unit (slave unit) have different communication modes, they will not be able to communicate properly.

- 2. Communication cannot be performed properly between a unit operating at an oscillator frequency of 6 MHz and another operating at 6.29 MHz, even when set to the same communication mode. Units must use the same oscillator frequency to be able to communicate.

#### 2.2.3 Communication Address

With the IEBus, each device is assigned a unique 12-bit communication address. The communication address consists of the following parts:

High-order 4 bits: Group number (number identifying the group to which a device belongs)Low-order 8 bits: Unit number (number identifying a device in a group)

#### 2.2.4 Broadcast

In ordinary communication, transmission and reception are performed between one master unit and one associated slave unit. Broadcast can also be done between one master unit and more than one slave unit. In this case master unit transmits data to an arbitrary number of slave units. In this case, the slave units do not return on acknowledge signal to the master unit.

Whether the communication to be performed is broadcast or ordinary communication is determined by the setting of the broadcast bit. (For details of the broadcast bit, see (1) (2) in Section 2.3.)

There are two types of broadcast.

#### (1) Group broadcast

Broadcast is performed to the devices in a particular group. These devices all have the same group number, as indicated by the high-order 4 bits of each communication address.

#### (2) General broadcast

Broadcast is performed to all devices, regardless of their group numbers.

These two types of broadcast are distinguished by the slave address. (For details of the slave address, see (3) in Section 2.3.)

#### 2.3 TRANSMISSION PROTOCOL

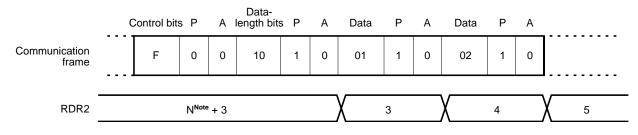

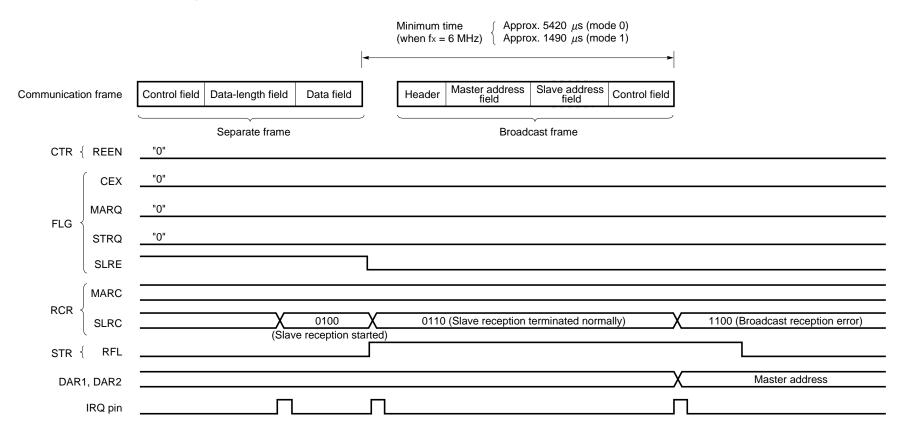

Fig. 2-1 shows the IEBus transmission signal format.

Communication data is transmitted as a sequence of signals called a communication frame. The transmission speed and the maximum amount of data that can be transmitted in one communication frame depend on the communication mode.

Fig. 2-1 Transmission Signal Format

(When  $f_x = 6 \text{ MHz}$ )

|       | ld name<br>er of bits | Hea          | Header Master<br>address field<br>1 1 12 1  |                   | Slave<br>address field<br>12 1 1 |                  | Control field 4 1 1 |   | Data-length<br>field<br>8 1 1 |   | Data fi<br>8 1 1 |                         |   | ita fie |                               |   | 1 |  |              |   |   |

|-------|-----------------------|--------------|---------------------------------------------|-------------------|----------------------------------|------------------|---------------------|---|-------------------------------|---|------------------|-------------------------|---|---------|-------------------------------|---|---|--|--------------|---|---|

|       |                       | Start<br>bit | Broad-<br>cast<br>bit                       | Master<br>address | Ρ                                | Slave<br>address | Ρ                   | A | Control<br>bits               | Ρ | A                | Data-<br>length<br>bits | Ρ | A       | Data<br>bits                  | Ρ | A |  | Data<br>bits | Р | A |

| Trans | smission<br>time      |              |                                             |                   |                                  |                  |                     |   |                               |   |                  |                         |   |         |                               |   |   |  |              |   |   |

|       | Mode 0                |              | Approx. 7330 μs         Approx. 1590 × N μs |                   |                                  |                  |                     |   |                               |   |                  |                         |   |         |                               |   |   |  |              |   |   |

|       | Mode 1                |              | Approx. 2090 μs                             |                   |                                  |                  |                     |   |                               |   |                  |                         |   |         | Approx. 410 $	imes$ N $\mu$ s |   |   |  |              |   |   |

- P : Parity bit (1 bit)

- A : Acknowledge bit (1 bit)

When A = 0: ACK

When A = 1: NAK

N : Number of data bytes

Remark For broadcast, the value of the acknowledge bit is ignored.

#### (1) Header

The header consists of a start bit and a broadcast bit. These are explained below.

#### 1 Start bit

The start bit is a signal used to notify the other units of the beginning of data transmission.

Before a unit starts data transmission, it outputs a low-level signal (start bit) for a specified duration, then outputs the broadcast bit.

When the unit attempts to output the start bit, another unit may have already output the start bit. In such a case, the unit does not output the start bit, and instead waits for the other unit to stop outputting the start bit. Then, synchronized with the completion of start bit output by the other unit, the unit starts output of the broadcast bit.

All units, except that unit which started the transmission, detect the start bit and become ready for reception.

#### 2 Broadcast bit

The broadcast bit is used to distinguish between broadcast and ordinary communication.

If the broadcast bit is 0, broadcast is indicated. If the broadcast bit is 1, ordinary communication is indicated. There are two types of broadcast: group broadcast and general broadcast. These types are distinguished by the slave address. (For details of the slave address, see **(3)**.)

For broadcast, more than one slave unit can exist as an associated communication station. Therefore, the acknowledge bits for the master address field and subsequent fields are not returned.

When more than one unit starts sending a communication frame at the same time, broadcast takes precedence over ordinary communication and wins arbitration.

## (2) Master address field

The master address field is used to transmit the local unit address (master address) to other units. The master address field consists of master address bits and a parity bit.

A master address consists of 12 bits. It is output starting with the MSB.

When more than one unit starts transmitting the same broadcast bit value at the same time, arbitration determination is performed by the master address field.

Each time a unit transmits one bit of the master address field, the unit compares its output data with the data on the bus. If the comparison indicates that the master address output by the unit differs from the data on the bus, the unit determines that it has lost an arbitration. The unit stops transmission, and readies itself for reception. The IEBus is organized by wired AND. When arbitration is performed between units (arbitration masters), the unit having the smallest master address value wins the arbitration.

After the 12-bit master address has been output, only one unit is finally determined as being the master unit, such that that unit remains in the transmission state.

Next, the master unit outputs a parity bit<sup>Note</sup> to post the master address to other units. Then, the master unit proceeds to the slave address field.

Note Even parity is used. When the number of 1's in the master address bits is odd, the parity bit is set to 1.

#### (3) Slave address field

The slave address field is used to transmit the address (slave address) of a unit (slave unit) with which the master unit wants to communicate.

The slave address field consists of slave address bits, a parity bit, and an acknowledge bit.

A slave address consists of 12 bits. It is output starting with the MSB. After a 12-bit slave address has been transmitted, a parity bit is output to prevent the slave address from being received incorrectly. Then, the master unit attempts to detect the acknowledge signal from a slave unit to confirm that the slave unit exists on the bus. When the acknowledge signal is detected, the master unit outputs a control field. Note, however, that when performing broadcast, the master unit outputs the control field without attempting to detect the acknowledge bit. The slave unit outputs an acknowledge signal when the slave unit recognizes a match between the slave unit's address and the slave address transmitted by the master unit match, and that both the master address and slave address have even parity. If the slave unit detects odd parity, it does not recognize the addresses as matching, so does not output an acknowledge signal. In this case, the master unit is placed in the standby (monitor) state, and communication terminates.

For broadcast, the slave address is used to distinguish between group broadcast or general broadcast, as follows:

When the slave address is FFFH: General broadcastWhen the slave address is other than FFFH: Group broadcast

**Remark** For group broadcast, the number of a target group is indicated by the high-order 4 bits of the slave address.

# (4) Control field

The control field indicates the type and direction of the next data field.

The control field consists of control bits, a parity bit, and an acknowledge bit.

The four control bits are output starting with the MSB.

Following the control bits, a parity bit is output. If even parity is detected, and the function requested by the master unit can be performed by the slave unit, the slave unit outputs an acknowledge signal. Then, the slave unit proceeds to the data-length field. If the slave unit cannot perform the processing requested by the master unit, even when even parity is detected, or if odd parity is detected, the slave unit does not output an acknowledge signal, and it enters the standby (monitor) state again.

After detecting the acknowledge signal, the master unit proceeds to the data-length field.

If an acknowledge signal is not detected, the master unit enters the standby state, terminating communication. For broadcast, however, the master unit proceeds to the next data-length field without attempting to detect the acknowledge signal.

Table 2-3 lists the meanings of the control bits.

# (5) Data-length field

The data-length field specifies the communication data length, in bytes.

The data-length field consists of the data-length bits, a parity bit, and an acknowledge bit.

The eight data-length bits are output starting with the MSB. The data-length bits indicate the communication data length, in bytes, as shown in Table 2-2.

| Data-length bit (hexadecimal) | Transmission data length, in bytes |

|-------------------------------|------------------------------------|

| 01H                           | 1                                  |

| 02H                           | 2                                  |

| :                             | :                                  |

| :                             | :                                  |

| FFH                           | 255                                |

| 00H                           | 256                                |

Table 2-2

Values of the Data-Length Bits and Their Meanings

**Remark** If the data length set in the data-length bits exceeds the maximum number of transmission bytes, the latter varying with the communication mode, more than one frame is transmitted. In the second and subsequent frames, the data-length bits indicate the remaining communication data length, in bytes.

The operation performed for this field differs depending on whether master transmission (when bit 3 of the control bits is 1) or master reception (when bit 3 of the control bits is 0) is performed.

# **1** Master transmission

The data-length bits and parity bit are output by the master unit. When the slave unit detects even parity, the slave unit outputs an acknowledge signal, then proceeds to the data field. For broadcast, however, the slave unit does not output an acknowledge signal.

If the slave unit detects odd parity, the slave unit does not output an acknowledge signal, regarding the received data-length bits as being incorrect. Then, the slave unit enters the standby (monitor) state again. At this time, the master unit also enters the standby state again, and communication terminates.

# (2) Master reception

The data-length bits and parity bit are output by the slave unit. When the master unit detects even parity, the master unit outputs the acknowledge signal.

If the master unit detects odd parity, the master unit does not output an acknowledge signal, regarding the received data-length bits as being incorrect. Then, the master unit enters the standby state again. At this time, the slave unit also enters the standby state again, and communication terminates.

#### (6) Data field

The data field is used for data transmission and reception to and from a slave unit.

The master unit uses the data field to transmit data to the slave unit, or to receive data from the slave unit. The data field consists of data bits, a parity bit, and an acknowledge bit.

The eight data bits are output, starting with the MSB.

After the data bits have been output, the parity bit and acknowledge bit are output from the master unit and slave unit, respectively.

Broadcast is performed only when the master unit transmits data. At this time, any acknowledge signal is ignored. The operations related to master transmission and master reception are explained below.

#### **1** Master transmission

When the master unit performs a write to a slave unit, the master unit transmits the data bits and a parity bit to the slave unit. The slave unit receives the data bits and parity bit, then outputs an acknowledge signal if even parity is detected and the reception buffer is empty. If odd parity is detected, or if the reception buffer is not empty, the slave unit rejects the corresponding data, and does not output an acknowledge signal.

If no acknowledge signal is received from the slave unit, the master unit transmits the same data again. The master unit repeats this operation until it receives an acknowledge signal from the slave unit, or until the data exceeds the maximum number of transmission bytes.

When even parity is detected, and an acknowledge signal is received from the slave unit, the master unit transmits the subsequent data, if any, and provided the maximum number of transmission bytes is not reached.

For broadcast, an acknowledge signal is not output by any slave unit. The master unit transfers data one byte at a time.

#### 2 Master reception

When the master unit reads data from a slave unit, the master unit outputs a synchronization signal for each bit as it is read.

The slave unit outputs data and a parity bit to the bus according to the synchronization signal output by the master unit.

The master unit reads the data and parity bit output by the slave unit, and checks the parity.

If the master unit detects odd parity, or if the reception buffer is not empty, the master unit rejects the data, and does not output an acknowledge signal. The master unit repeats the read operation for the same data provided the maximum allowable number of transmission bytes per communication frame has not been reached.

If the master unit confirms even parity, and the reception buffer is empty, the master unit accepts the data, and returns an acknowledge signal to the slave unit. Then, the master unit reads the next data, provided the maximum allowable number of transmission bytes per frame has not been reached.

# (7) Parity bit

A parity bit is used to check for errors in the transmission data.

A parity bit is added to the master address bits, slave address bits, control bits, data-length bits, and data bits. Even parity is used. If the number of 1's in the data is odd, the parity bit is set to 1. If the number of 1's in the data is even, the parity bit is set to 0.

# (8) Acknowledge bit

In ordinary communication (one-unit-to-one-unit communication), an acknowledge bit is added in the following positions to confirm that data has been received correctly:

- At the end of the slave address field

- At the end of the control field

- At the end of the data-length field

- At the end of the data field

The acknowledge bit is defined as follows:

- 0: Indicates that transmission data has been recognized. (ACK)

- 1: Indicates that no transmission data has been recognized. (NAK)

For broadcast, the acknowledge bit is ignored.

#### (1) Acknowledge bit at the end of the slave address field

If any of the following is detected, the acknowledge bit at the end of the slave address field is set to NAK, and transmission is stopped:

- The parity of the master address bits or slave address bits is incorrect.

- A timing error occurred (bit format error).

- No slave unit is found.

#### (2) Acknowledge bit at the end of the control field

If any of the following is detected, the acknowledge bit at the end of the control field is set to NAK, and transmission is stopped:

- The parity of the control bits is incorrect.

- Although the slave reception buffer<sup>Note</sup> is not empty, bit 3 of the control bits is 1 (write operation).

- Although the slave transmission buffer<sup>Note</sup> is empty, the control bits indicate data read (3H, 7H).

- For a locked unit, a unit other than the unit that specified the lock makes a request by using control bits indicating 3H, 6H, 7H, AH, BH, EH, or FH.

- Although no lock has been set, control bits indicating lock address read (4H) are set.

- A timing error occurred.

- An undefined control bit setting has been made.

Note See (1) in Section 2.4.

#### **3** Acknowledge bit at the end of the data-length field

If any of the following is detected, the acknowledge bit at the end of the data-length field is set to NAK, and transmission is stopped:

- The parity of the data-length bits is incorrect.

- A timing error occurred.

#### (4) Acknowledge bit at the end of the data field

If any of the following is detected, the acknowledge bit at the end of the data field is set to NAK, and transmission is stopped:

- The parity of the data bits is incorrectNote.

- A timing error occurred after the previous acknowledge bit.

- The reception buffer is full, such that no more data can be accepted<sup>Note</sup>.

- **Note** In this case, if the maximum allowable number of transmission bytes per frame has not yet been reached, the transmitter retries transmission of the data field until the maximum number of transmission bytes is reached.

#### 2.4 TRANSMISSION DATA (CONTENTS OF THE DATA FIELD)

The contents of the data field are indicated by the control bits.

|    | Bit 3Note 1 | Bit 2 | Bit 1 | Bit 0 | Function <sup>Note 2</sup>            |

|----|-------------|-------|-------|-------|---------------------------------------|

| он | 0           | 0     | 0     | 0     | Read slave status (SSR)               |

| 1H | 0           | 0     | 0     | 1     | Undefined                             |

| 2H | 0           | 0     | 1     | 0     | Undefined                             |

| ЗН | 0           | 0     | 1     | 1     | Read data and locking                 |

| 4H | 0           | 1     | 0     | 0     | Read lock address (low-order 8 bits)  |

| 5H | 0           | 1     | 0     | 1     | Read lock address (high-order 4 bits) |

| 6H | 0           | 1     | 1     | 0     | Read slave status (SSR) and unlocking |

| 7H | 0           | 1     | 1     | 1     | Read data                             |

| 8H | 1           | 0     | 0     | 0     | Undefined                             |

| 9H | 1           | 0     | 0     | 1     | Undefined                             |

| AH | 1           | 0     | 1     | 0     | Write command and locking             |

| BH | 1           | 0     | 1     | 1     | Write data and locking                |

| СН | 1           | 1     | 0     | 0     | Undefined                             |

| DH | 1           | 1     | 0     | 1     | Undefined                             |

| EH | 1           | 1     | 1     | 0     | Write command                         |

| FH | 1           | 1     | 1     | 1     | Write data                            |

Table 2-3 Meanings of the Control Bits

**Notes 1.** The transfer direction of the data-length bits of the subsequent data-length field and data in the data field changes according to the value of bit 3 (MSB).

When bit 3 is 1: Transfer from the master unit to the slave unit

When bit 3 is 0: Transfer from the slave unit to the master unit

The values of control bits 3H, 6H, AH, and BH specify locking and unlocking. When an undefined value, 1H, 2H, 8H, 9H, CH, or DH, is transmitted, no acknowledge signal is returned.

Once a unit has been locked by a master unit, the locked unit rejects the control bits received from other than the master unit that requested the lock, unless the value of the control bits is one of the values listed in Table 2-4. Then, the unit does not output the acknowledge bit.

|    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function                              |

|----|-------|-------|-------|-------|---------------------------------------|

| 0H | 0     | 0     | 0     | 0     | Read slave status                     |

| 4H | 0     | 1     | 0     | 0     | Read lock address (low-order 8 bits)  |

| 5H | 0     | 1     | 0     | 1     | Read lock address (high-order 4 bits) |

#### (1) Reading the slave status (SSR) (control bits: 0H, 6H)

A master unit can read the slave status (0H, 6H) to determine why the slave unit did not return the acknowledge bit (ACK).

The slave status is determined from the result of the communication last performed by the slave unit.

All slave units can provide slave status information.

Table 2-5 lists the slave status meanings.

#### Fig. 2-2 Slave Status (SSR) Bit Format

| MSB   |       |       |       |       |       |       | LSB   |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |

| Bit                     | Value | Meaning                                 |                                    |  |  |  |  |

|-------------------------|-------|-----------------------------------------|------------------------------------|--|--|--|--|

| Bit 0 <sup>Note 1</sup> | 0     | The slave transmission buffer is empty. |                                    |  |  |  |  |

|                         | 1     | The slave transmission buffer is        | not empty.                         |  |  |  |  |

| Bit 1 <sup>Note 2</sup> | 0     | The slave reception buffer is emp       | oty.                               |  |  |  |  |

|                         | 1     | The slave reception buffer is not       | empty.                             |  |  |  |  |

| Bit 2                   | 0     | The unit is not locked.                 |                                    |  |  |  |  |

|                         | 1     | The unit is locked.                     |                                    |  |  |  |  |

| Bit 3                   | 0     | Fixed at 0                              |                                    |  |  |  |  |

| Bit 4 <sup>Note 3</sup> | 0     | Slave transmission disabled             |                                    |  |  |  |  |

|                         | 1     | Slave transmission enabled              |                                    |  |  |  |  |

| Bit 5                   | 0     | Fixed at 0                              | Indicates the highest              |  |  |  |  |

| Bit 7                   | 00    | Mode 0                                  | mode supported by the unit Note 4. |  |  |  |  |

| Bit 6                   | 01    | Mode 1                                  |                                    |  |  |  |  |

|                         | 10    | Reserved for future expansion           |                                    |  |  |  |  |

|                         | 11    |                                         |                                    |  |  |  |  |

Table 2-5

Slave Status Meanings

- **Notes 1.** The slave transmission buffer is accessed during a data read operation (control bits: 3H, 7H). For the  $\mu$ PD72042B, this buffer corresponds to the TBF available when STRQ of the FLG register is set to 1.

- The slave reception buffer is accessed during a data write operation (control bits: 8H, AH, BH, EH, FH). For the μPD72042B, this buffer corresponds to the RBF available when SLRE of the FLG register is set to 1.

- 3. The value of bit 4 can be selected by using the UAR1 register.

- **4.** Bits 7 and 6 are currently fixed to 10 in the hardware of the  $\mu$ PD72042B.

#### (2) Data/command transfer (control bits: Read (3H, 7H), write (AH, BH, EH, FH))

When data read (3H, 7H) is set, the data in the data buffer of the slave unit is read into the master unit. When data write (BH, FH) or command write (AH, EH) is set, the data received by the slave unit is processed according to the operation specifications for the slave unit.

- Remarks 1. The user can select data and commands as necessary according to the system.

- 2. 3H, AH, and BH may cause locking, depending on the communication conditions and status.

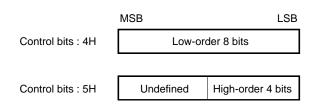

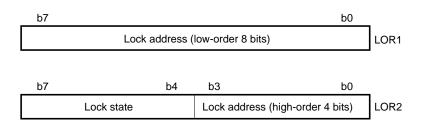

## (3) Reading a lock address (control bits: 4H, 5H)

When a lock address read operation (4H, 5H) is specified, the address (12 bits) of the master unit that issued the lock instruction is read in one-byte form, as shown below.

Fig. 2-3 Lock Address Format

# (4) Locking and unlocking (control bits: Locking (3H, AH, BH), unlocking (6H))

The lock function is used to enable the transfer a message using more than one communication frame. When locked, a unit cannot receive data from other than the unit that requested the lock. Locking and unlocking are performed as follows:

## 1 Locking

The master unit can lock the slave unit by specifying the lock with the corresponding control bits (3H, AH, BH). In this case, when the transmission or reception of acknowledge bit 0 for the data-length field has been completed, but the communication frame is then terminated before transmission or reception of as many data bytes as are specified by the data-length bits is completed, the slave unit is locked. At this time, the bit indicating the lock status (bit 2) in the slave status byte is set to 1.

#### 2 Unlocking

The master unit can unlock a locked slave unit when the control bits specify locking (3H, AH, or BH) or unlocking (6H). The slave unit is unlocked once as many data bytes as are specified by the data-length bits have been transmitted or received within one communication frame. At this time, the bit indicating the lock status (bit 2) in the slave status byte is reset to 0.

For broadcast, locking or unlocking is not performed.

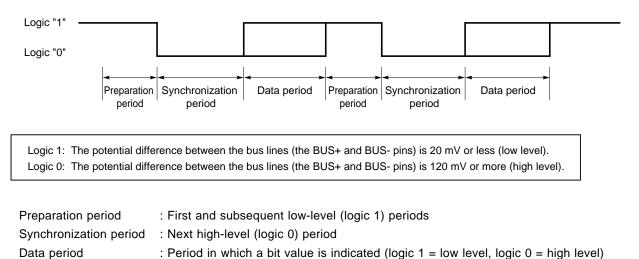

# 2.5 BIT FORMAT

Fig. 2-4 illustrates the bits that constitute an IEBus communication frame.

Fig. 2-4 IEBus Bit Format (Concept)

The synchronization and data periods are almost equal in duration.

For the IEBus, synchronization is established for each bit. The specifications of the total time required for a bit and the duration of each period allotted within the bit vary depending on the type of the transmission bits, and whether the unit is a master or slave.

# 3. MICROCOMPUTER INTERFACE

#### 3.1 TRANSFER METHOD

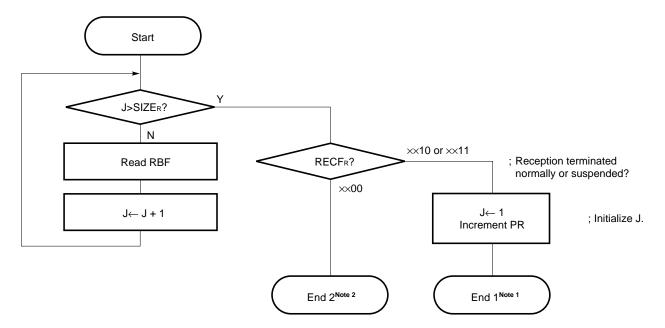

Either of two microcomputer interface modes can be selected: three-wire serial I/O mode or two-wire serial I/O mode.

Whether three-wire serial I/O mode or two-wire serial I/O mode is selected depends on the input level of the SEL pin (pin 12). (See Section 3.3 for details.)

SEL  $\leftarrow$  1: Three-wire serial I/O SEL  $\leftarrow$  0: Two-wire serial I/O

#### (1) Three-wire serial I/O (SEL $\leftarrow$ 1)

Three wires are used to read and write data. The three wires are the serial clock input ( $\overline{SCK}$ ), serial data input ( $SI^{Note 1}$ ), and serial data output ( $SO^{Note 2}$ ).

# (a) Read operation

Data is output to the SO pin upon detecting the falling edge of the  $\overline{SCK}$  pin.

# (b) Write operation

Data is input via the SI pin upon detecting the rising edge of the SCK pin. At this time, 1 is output on the SO pin.

# (2) Two-wire serial I/O (SEL $\leftarrow$ 0)

Two wires are used to read and write data. The two wires are the serial clock input ( $\overline{SCK}$ ) and serial data I/O (SIO<sup>Note 1</sup>).

#### (a) Read operation

The SIO pin is placed in the output state, and data is output upon detecting the falling edge of the SCK pin.

#### (b) Write operation

The SIO pin is placed in the input state, and data is input upon detecting the rising edge of the SCK pin.

#### Notes 1. The SI pin for three-wire serial I/O mode is also used as the SIO pin for two-wire serial I/O mode.

2. The impedance of the SO pin for three-wire serial I/O mode goes high in two-wire serial I/O mode. So, connect the SO pin to GND or V<sub>DD</sub>.

| RESET | CS | SEL | C/D |          | SO   |                     | State                  |

|-------|----|-----|-----|----------|------|---------------------|------------------------|

| RESET | 65 | SEL | C/D | SI (SIO) | 30   | Three-wire/two-wire | Operating mode         |

| 0     | ×  | ×   | ×   | I        | Hi-Z | _                   | Reset state            |

| 1     | 1  | ×   | ×   | I        | Hi-Z | _                   | Chip nonselected state |

| 1     | 0  | 1   | 1   | I        | O*   | Three-wire          | Control mode           |

|       |    |     | 0   |          |      |                     | Data write mode        |

|       |    |     |     |          | 0    |                     | Data read mode         |

|       |    | 0   | 1   | I        | Hi-Z | Two-wire            | Control mode           |

|       |    |     | 0   |          |      |                     | Data write mode        |

|       |    |     |     | 0        |      |                     | Data read mode         |

X

Table 3-1 I/O States of the SIO (SI) and SO Pins

I : Input state

Hi-Z : High-impedance state

: Don't care

- O : Output state

- $O^{\star}\,$  : State in which 1 is output

#### 3.2 DATA TRANSFER FORMAT

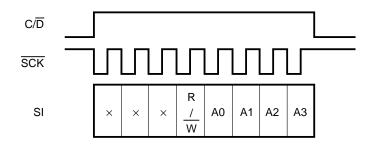

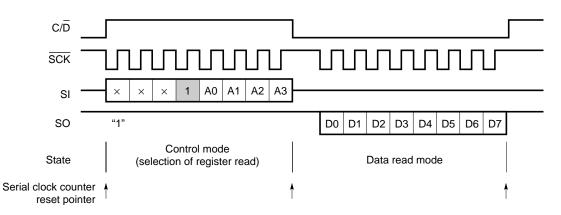

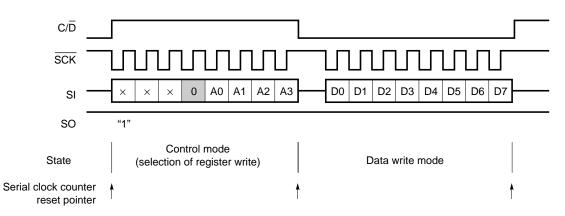

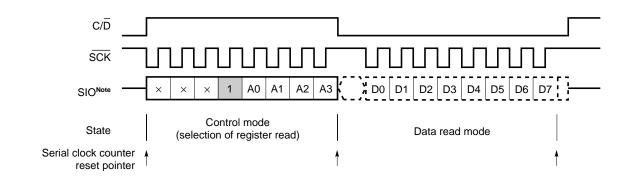

3.2.1 Three-Wire Data Transfer (SEL = 1)

#### (1) Control mode

When the  $C/\overline{D}$  input is set high, control mode is set to control data transfer. Data transfer control involves the following processing.

- (1) Register address setting

- 2 Register read/write selection

**Remark** After reset (RESET) cancellation, the state enabling writing to the register at address 0000B is set.

Caution In control mode, each data item is read every eighth clock pulse. (Data of less than eight clock periods is ignored.)

# (2) Data read mode

When the C/ $\overline{D}$  pin is set low after register read is selected in control mode, the data read mode is set. In data read mode, the data in a read register is read on the SO pin upon detecting the falling edge of the  $\overline{SCK}$  pin.

Caution When the  $C/\overline{D}$  pin is set high in data read mode, the serial clock counter is reset. Therefore, the remaining bits of the byte cannot be read; at the next falling edge, read is performed starting from the next byte in the case of RBF, or from the first bit for other registers.

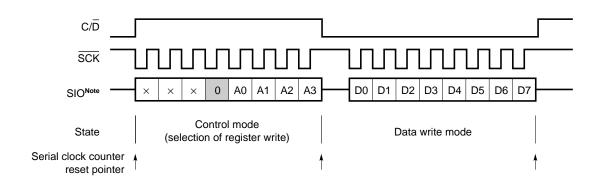

#### (3) Data write mode

When the C/ $\overline{D}$  pin is set low after register write has been selected in control mode, data write mode is set. In data write mode, data for a write register is applied to the SI pin at the rising edge of the  $\overline{SCK}$  pin.

Caution Register overwrite is started immediately after the eighth clock rising edge. All registers other than TBF are overwritten on the eighth clock rising edge. (Data of less than eight clock periods is ignored.)

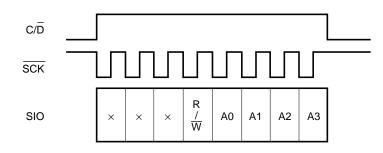

# 3.2.2 Two-Wire Data Transfer (SEL = 0)

#### (1) Control mode

When the  $C/\overline{D}$  input is set high, control mode is set to control data transfer. Data transfer control involves the following processing.

- 1 Register address setting

- (2) Register read/write selection

**Remark** After reset (RESET) cancellation, the state enabling writing to the register at address 0000B is set.

Caution In control mode, each data item is read every eighth clock pulse. (Data of less than eight clock periods is ignored.)

#### (2) Data read mode

- Note —— SIO pin input state

- Cautions 1. When the C/D pin is set high in data read mode, the serial clock counter is reset. Therefore, the remaining bits of the byte cannot be read; at the next falling edge, a read operation is performed starting from the next byte in the case of RBF, or from the first bit for other registers.

- 2. The SIO pin is a CMOS I/O pin. So, be careful to avoid an output collision between the SIO pin and the microcomputer. Further, a pull-up resistor is required when N-ch open-drain output of the microcomputer is used. Note that if the last output level is low upon the termination of read mode, current will flow constantly.

# (3) Data write mode

- Note \_\_\_\_\_ SIO pin input state

- Caution Register overwrite is started immediately after the eighth clock rising edge. All registers other than TBF are overwritten at the eighth clock rising edge. (Data of less than eight clock periods is ignored.)

# 3.3 CONNECTION TO A MICROCOMPUTER

#### (1) Three-wire serial I/O

#### (2) Two-wire serial I/O

- **Notes 1.** When only the  $\mu$ PD72042B is to be controlled from a microcomputer via a serial I/O interface, the  $\overline{CS}$  pin must be tied low (by connecting it to GND).

- 2. When an interrupt is detected by polling (in FLG register read), IRQ may be left open. When high-volume or high-speed data transfer is required, however, the system described above is recommended to ensure reliable data transfer.

- **3.** Required when the microcomputer's N-ch open-drain output is used. The SIO pin of the  $\mu$ PD72042B is a CMOS I/O pin.

# 3.4 STANDBY MODE SETTING AND CANCELLATION

Standby mode can be set by setting STREQ of the CTR register to 1. The XI pin for oscillation is tied to GND, and the impedance of the XO pin goes high.

In standby mode (with the STM flag of the FLG register set to 1), only the following registers can be accessed:

Writable register : CTR (address 0000B) Readable register : FLG (address 0001B)

Standby mode can be cancelled by setting STREQ of the CTR register to 0.

Caution Do not read any data from internal registers via the serial I/O during the period from when a microcomputer sets the STREQ flag to 1 to when the  $\mu$ PD72042B enters the standby mode. This period is one-communication frame at maximum.

## 3.5 RESET MODE SETTING AND CANCELLATION

For hardware reset, the registers are initialized and standby mode is set. (During this period, oscillation is stopped.) For software reset, the registers are initialized, and operation is started.

# 4. REGISTERS

A microcomputer controls IEBus communication by reading from and writing to the internal registers of the  $\mu$ PD72042B.

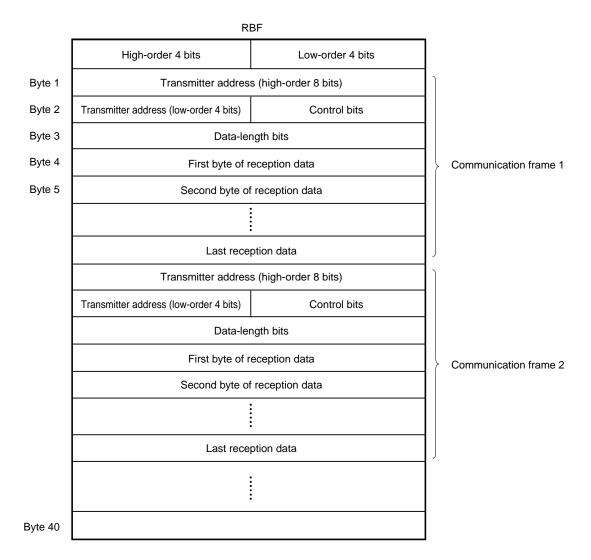

Registers are classified into write registers and read registers. The total size of the write registers is 40 bytes; the transmission buffer uses 33 of the 40 bytes. The total size of the read registers is 49 bytes; the reception buffer uses 40 of the 49 bytes.

Table 4-1 lists the registers.

#### Table 4-1 µPD72042B Registers

#### (a) Write registers

| $\searrow$ | Address | Name | High-order 4 bits                   |            |           |                  | Low-order 4 bits |                |         | Note  | Reference page |       |

|------------|---------|------|-------------------------------------|------------|-----------|------------------|------------------|----------------|---------|-------|----------------|-------|

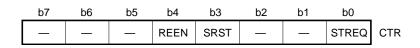

| он         | 0000    | CTR  | -                                   | Ι          | -         | – REEN           |                  | -              | -       | STREQ | А              | p. 31 |

| 1H         | 0001    | CMR  | 0                                   | LOCK       | BU        | IFC              |                  | СО             | МС      |       | С              | p. 32 |

|            |         |      | 1 0 0 0                             |            |           | 0                | IRS              | MFC            | DERC    |       |                |       |

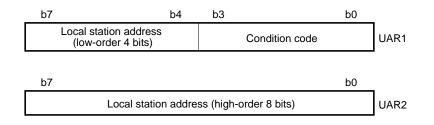

| 2H         | 0010    | UAR1 |                                     | cal statio |           |                  |                  | Condition code |         |       | В              | p. 34 |

| ЗН         | 0011    | UAR2 |                                     | Loca       | l statior | n addres         | s (high-         | order 8        | bits)   |       | В              | p. 34 |

| 4H         | 0100    | SAR1 | Slave address<br>(low-order 4 bits) |            |           |                  | 0                | 0              | 0       | 0     | D              | p. 35 |

| 5H         | 0101    | SAR2 |                                     | S          | lave ad   | ldress (h        | nigh-ord         | er 8 bits      | ;)      |       | D              | p. 35 |

| 6H         | 0110    | MCR  | Broadc                              | ast bits   |           | ber of<br>ations |                  | Contr          | ol bits |       | D              | p. 36 |

| 7H         | 0111    | -    | _                                   |            |           |                  |                  |                |         | -     | _              |       |

| 8H         | 1000    | _    | _                                   |            |           |                  |                  |                | _       | _     |                |       |

| EH         | 1110    | TBF  | Num                                 | per of by  | /tes of t | ransmis          | sion da          | ta, trans      | missior | data  | F              | p. 38 |

#### (b) Read registers

| $\square$ | Address | Name | ł   | ligh-ord                                  | ler 4 bit | 5                     | Low-order 4 bits |                    |        |       | Note  | Reference page |

|-----------|---------|------|-----|-------------------------------------------|-----------|-----------------------|------------------|--------------------|--------|-------|-------|----------------|

| он        | 0000    | STR  | TFL | TEP                                       | RFL       | REP                   |                  | -                  | -      |       | A     | p. 39          |

| 1H        | 0001    | FLG  | -   | MARQ                                      | STRQ      | SLRE                  | CEX              | RAW                | STM    | IRQ   | A     | p. 40          |

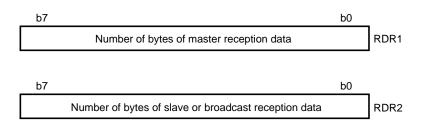

| 2H        | 0010    | RDR1 |     | Numb                                      | per of by | tes of n              | naster r         | eceptior           | data   |       | A     | p. 42          |

| ЗH        | 0011    | RDR2 |     | Numb                                      |           | tes of sl<br>dcast re |                  | •                  | ata or |       | A     | p. 42          |

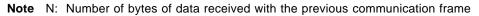

| 4H        | 0100    | LOR1 |     |                                           | Lock ad   | dress (le             | ow-orde          | r 8 bits)          |        |       | н     | p. 43          |

| 5H        | 0101    | LOR2 |     | Lock                                      | state     |                       | (1               | Lock a<br>high-ord |        | 6)    | н     | p. 43          |

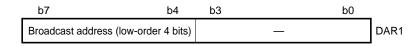

| 6H        | 0110    | DAR1 | -   | Broadcast address –<br>(low-order 4 bits) |           |                       |                  |                    |        | E     | p. 44 |                |

| 7H        | 0111    | DAR2 |     | Broadcast address (high-order 8 bits)     |           |                       |                  |                    |        | E     | p. 44 |                |

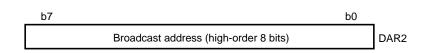

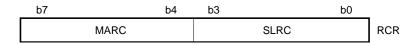

| 8H        | 1000    | RCR  |     | Return codes (MARC, SLRC)                 |           |                       |                  |                    | А      | p. 45 |       |                |

| EH        | 1110    | RBF  |     | Tra                                       | ansmitte  | er addre              | ss, rece         | ption da           | ata    |       | G     | p. 57          |

Note Writable and readable periods of the registers of the  $\mu$ PD72042B

- A: Arbitrary

- B: After system reset cancellation

- C: While CEX of the FLG register (address 0001) is set to 0

- D: While MARQ of the FLG register (address 0001) is set to 0

- E: After SLRC of the RCR register (address 1000) is set to 1100 (broadcast reception error)

- F: While TFL of the STR register (address 0000) is set to 0

- G: While REP of the STR register (address 0000) is set to 0

- H: When CEX of the FLG register (address 0001) is set to 0 after LOCK of the CMR register (address 0001) is set to 1

Cautions 1. In standby mode (with STM of the FLG register set to 1), the user can only write to the CTR register (including standby mode cancellation) and read from the FLG register.

- 2. Never access a free address.

- 3. Slave status (SSR) can be read into RBF by setting the control bits to 0H or 6H from the master unit.

| CTR              | Address : 0000B (0H)   |

|------------------|------------------------|

|                  | Read/write : Write     |

| Control register | When reset : xxx00xx1B |

CTR is a one-byte write register used to control  $\mu$ PD72042B operations.

# [REEN]

When REEN is set to 1, the SLRE flag of the FLG register is immediately set to 1 to enable both slave and broadcast reception.

# [SRST]

When SRST is set to 1, the µPD72042B is immediately reset. (Note, however, that STREQ is set to a written value.)

# [STREQ]

- 1: Requests standby mode.

- 0: Exits from standby mode.

#### • Standby mode setting and cancellation

The  $\mu$ PD72042B is requested to enter the standby mode by setting the STREQ flag to 1 from the microcomputer. The  $\mu$ PD72042B enters standby mode when the standby mode input enabled state (carrier sense state) is set. In this case, the impedance of the BUS+ and BUS– pins goes high (logic 1), and the STM flag of the FLG register is set to 1. In standby mode, oscillation is stopped, and all operations are stopped while preserving the internal data, thus minimizing power consumption.

When, in standby mode, the STREQ flag is set to 0 from the microcomputer, standby mode is cancelled after the period (about 20 ms at fx = 6 MHz) needed for oscillation to stabilize; the halted operations are resumed from the point at which standby mode was set. At this time, the STM flag of the FLG register changes to 0. In standby mode, <u>only writing to the CTR register (for standby mode cancellation) and reading from the FLG register</u> can be performed from the microcomputer.

can be performed from the microcomputer.

- Cautions 1. When the SRST flag and STREQ flag are simultaneously set to 1, standby mode is set after software reset. (This state is the same as that set by hardware reset.) Note, however, that when the SRST flag is set to 1 in standby mode, a software reset is performed, but this is not reflected in the FLG register.

- 2. Do not read any data from internal registers via the serial I/O during the period from when a microcomputer sets the STREQ flag to 1 to when the  $\mu$ PD72042B enters the standby mode. This period is one-communication frame at maximum.

| CMR              | Address : 0001B (1H)   |

|------------------|------------------------|

|                  | Read/write : Write     |

| Command register | When reset : 00000000B |

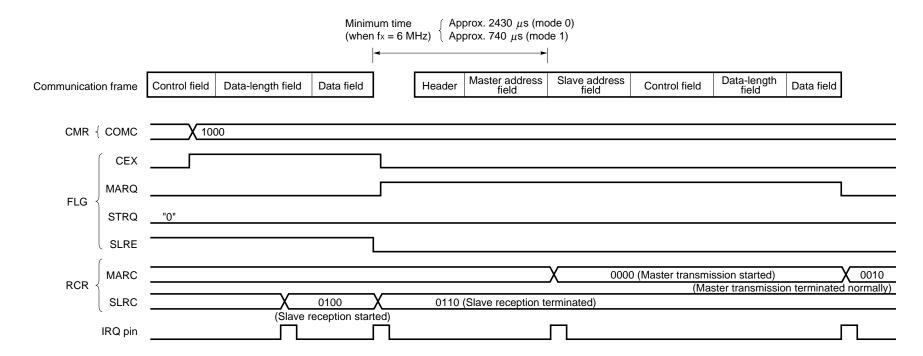

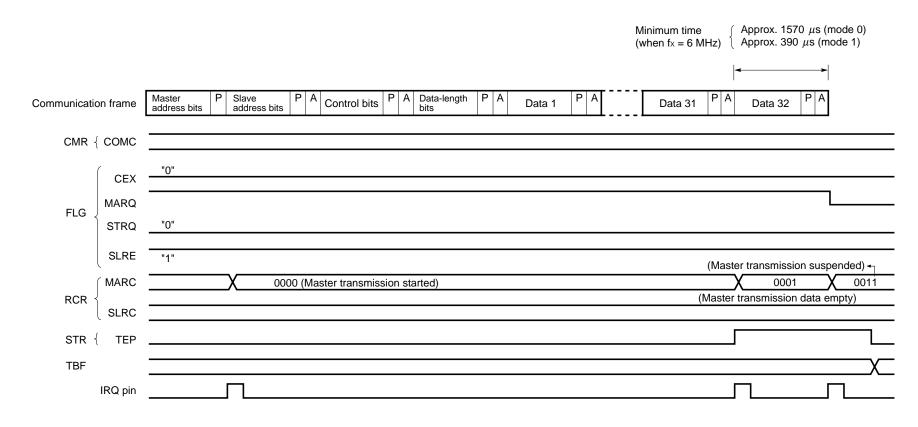

CMR is a one-byte write register used to set a command for communication control, transmission/reception buffer control, or optional function setting.

When data is set in CMR from the microcomputer, CEX of the FLG register is set to 1. When the  $\mu$ PD72042B processes the data set in CMR, CEX is set to 0.

After the microcomputer checks that CEX of the FLG register is set to 0, new data can be set in CMR. The following describes the data that is set in CMR.

#### (1) When bit 7 (MSB) of CMR is 0

| b7 | b6   | b5 | b4 | b3 |      | b0 |     |

|----|------|----|----|----|------|----|-----|

| 0  | LOCK | BU | FC |    | COMC |    | CMR |

#### [LOCK]: Lock state setting command

- 1 : The value representing the lock state (0001 for locked or 0000 for not-locked) and lock address are output to LOR1 and LOR2. Note, however, that when 0000 (not-locked) is output, any lock address value is ignored.

- 0 : The contents of LOR1 and LOR2 remain as is.

[BUFC]: Transmission/reception buffer control command

- 00 : The transmission and reception buffers remain as is.

- 01 : The transmission buffer (TBF) is cleared.

- 10 : The reception buffer (RBF) is cleared.

- 11 : The data of the previous (latest) communication frame to be stored in the reception buffer (RBF) is cleared<sup>Note 1</sup>.

#### [COMC]: Communication control command

- 0000: Communication operation remains as is.

- 0001: The locked state is cancelled.

- 1000: Master communication is requested Note 2.

- 1001: Master communication is requested, with the previous master transmission state held<sup>Note 3</sup>.

- 1010: Master communication is aborted.

- 1011: Slave data transmission is requested Note 4.

- 1100: Slave data transmission is requested, with the previous slave data transmission state heldNote 5.

- 1101: Slave data transmission is aborted.

- 1111: Slave reception and broadcast reception are disabled.

- **Notes 1.** If the microcomputer has already read the data for the previous (latest) communication frame from RBF, or optional function setting in CMR is selected and MFC = 0, clear RBF with BUFC = 10.

- **Notes 2.** When the MSB of the control bits set in MCR is 1 (for master transmission), set the number of bytes of transmission data, and at least one byte of transmission data in TBF before command setting.

- **3.** When the MSB of the control bits set in MCR is 1 (for master transmission), set at least one byte of transmission data before command setting. This operation is not required if all transmission data has already been set in TBF.

- 4. Set the number of bytes of transmission data, and at least one byte of transmission data in TBF before command setting.

- **5.** Set at least one byte of transmission data in TBF before command setting. This operation is not required if all transmission data has already been set in TBF.

# (2) When bit 7 (MSB) of CMR is 1

An optional function is set.

| _ | b7 | b6 | b5 | b4 | b3 | b2  | b1  | b0   |     |

|---|----|----|----|----|----|-----|-----|------|-----|

|   | 1  | 0  | 0  | 0  | 0  | IRS | MFC | DERC | CMR |

[MFC]: Selection of one frame/multiple frames

- 1 : Data for multiple frames is stored in RBF.

- 0 : Data for only one frame is stored in RBF.

[DERC]: Broadcast reception selection

- 1 : The issue of return code 1100 (broadcast reception error) for SLRC of the RCR register is enabled.

- 0 : The issue of return code 1100 (broadcast reception error) for SLRC of the RCR register is disabled.

**[IRS]**: Interrupt generation condition selection

- $\mathbf{0}$  : An interrupt is requested when the data of the RCR register changes.

- 1 : An interrupt is requested when the data of the RCR register changes to other than the following: MARC = 0000B (start of master transmission)

- MARC = 0100B (start of master reception)

- SLRC = 0000B (start of slave data transmission)

- SLRC = 0100B (start of slave reception)

- SLRC = 1000B (start of broadcast reception)

Caution Set an optional function in initialization processing after reset cancellation for the  $\mu$ PD72042B. Until an optional function has been set, the  $\mu$ PD72042B will not accept IEBus communication.

| UAR1<br>UAR2                        | Address : 0010B (2H) (UAR1)<br>0011B (3H) (UAR2) |

|-------------------------------------|--------------------------------------------------|

|                                     | Read/write : Write                               |

| Local station unit address register | When reset : Undefined (with the                 |

|                                     | previous data held)                              |

UAR1 and UAR2 are registers used to set a local station unit address (12 bits) and condition code. Set UAR1 and UAR2 after reset cancellation.

#### [Local station address]

A local station address is used as a master address when the local station performs communication as the master unit. A local station address is used as a slave address when the local station performs communication as a slave.

#### [Condition code]

| Bit position | Condition code | Condition setting                           |  |  |

|--------------|----------------|---------------------------------------------|--|--|

| b3, b2       | 00             | Communication is performed in mode 0.       |  |  |

|              | 01             | Communication is performed in mode 1.       |  |  |

|              | 10             | Undefined                                   |  |  |

|              | 11             |                                             |  |  |

| b0 0         |                | The slave transmission section is disabled. |  |  |

|              | 1              | The slave transmission section is enabled.  |  |  |

**Remark** Bit 1 of a condition code is not used. (Set the bit to either 0 or 1.)

| SAR1<br>SAR2           | Address : 0100B (4H) (SAR1)<br>0101B (5H) (SAR2)                            |

|------------------------|-----------------------------------------------------------------------------|

| Slave address register | Read/write :Write<br>When reset :Undefined (the pre-<br>vious data is held) |

|                        | viede data ie heidy                                                         |

The SAR1 and SAR2 registers are used to set the address of a remote station (slave address) in master communication.

Set SAR1 and SAR2 while the value of MARQ of the FLG register is 0 (while master communication is not requested).

| b7                                | b4             | b3 |   |   | b0 | _    |

|-----------------------------------|----------------|----|---|---|----|------|

| Slave address (low                | -order 4 bits) | 0  | 0 | 0 | 0  | SAR1 |

|                                   |                |    |   |   |    | -    |

| b7                                |                |    |   |   | b0 | _    |

| Slave address (high-order 8 bits) |                |    |   |   |    |      |

| MCR                           | Address : 0110B (6H)             |

|-------------------------------|----------------------------------|

|                               | Read/write : Write               |

| Master communication register | When reset : Undefined (the pre- |

|                               | vious data is held)              |

|                               |                                  |

The MCR register is used to set a master communication condition.

Set MCR while the value of MARQ of the FLG register is 0 (while master communication is not requested).

| b7            | b6        | b4           | b3 | b0           | _   |

|---------------|-----------|--------------|----|--------------|-----|

| Broadcast bit | Number of | arbitrations |    | Control bits | MCR |

# [Broadcast bit]

This bit is used to select broadcast or separate communication.

Bit 7 = 0: Broadcast

Bit 7 = 1: Separate communication

#### [Number of arbitrations] (Number of retries)

This field is used to set the maximum number of retry operations to be performed if arbitration is lost in master communication. The  $\mu$ PD72042B automatically retries communication as many times as the number set in this field.

| b6 | b5 | b4 | Number of retries |

|----|----|----|-------------------|

| 0  | 0  | 0  | 0                 |

| 0  | 0  | 1  | 1                 |

| 0  | 1  | 0  | 2                 |

| 0  | 1  | 1  | 3                 |

| 1  | 0  | 0  | 4                 |

| 1  | 0  | 1  | 5                 |

| 1  | 1  | 0  | 6                 |

| 1  | 1  | 1  | 7                 |

# [Control bits]

This control field is used to set the control bits (four bits).

# Contents of control bits

|    | Bit 3Note 1 | Bit 2 | Bit 1 | Bit 0 | Function <sup>Note 2</sup>            |

|----|-------------|-------|-------|-------|---------------------------------------|

| 0H | 0           | 0     | 0     | 0     | Slave status (SSR) read               |

| 1H | 0           | 0     | 0     | 1     | Undefined                             |

| 2H | 0           | 0     | 1     | 0     | Undefined                             |

| ЗН | 0           | 0     | 1     | 1     | Data read and lock                    |

| 4H | 0           | 1     | 0     | 0     | Lock address read (low-order 8 bits)  |

| 5H | 0           | 1     | 0     | 1     | Lock address read (high-order 4 bits) |

| 6H | 0           | 1     | 1     | 0     | Slave status (SSR) read and unlock    |

| 7H | 0           | 1     | 1     | 1     | Data read                             |

| 8H | 1           | 0     | 0     | 0     | Undefined                             |

| 9Н | 1           | 0     | 0     | 1     | Undefined                             |

| AH | 1           | 0     | 1     | 0     | Command write and lock                |

| вн | 1           | 0     | 1     | 1     | Data write and lock                   |

| СН | 1           | 1     | 0     | 0     | Undefined                             |

| DH | 1           | 1     | 0     | 1     | Undefined                             |

| EH | 1           | 1     | 1     | 0     | Command write                         |

| FH | 1           | 1     | 1     | 1     | Data write                            |

**Notes 1.** The value of bit 3 (MSB) determines the transfer direction of the subsequent data-length field data and data field data.

When bit 3 is set to 1: Data is transferred from the master unit to a slave unit.

When bit 3 is set to 0: Data is transferred from a slave unit to the master unit.

**2.** 3H, 6H, AH, and BH are control bits used for lock setting and cancellation.

When an undefined value of 1H, 2H, 8H, 9H, CH, or DH is sent, no acknowledgement is returned.

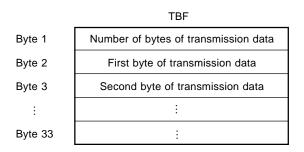

| TBF                 | Address : 1110B (EH) |  |

|---------------------|----------------------|--|

|                     | Read/write : Write   |  |

| Transmission buffer | When reset : Empty   |  |

TBF is a 33-byte FIFO buffer used to hold the number of bytes of transmission data and transmission data for master transmission and slave data transmission.

TBF can be written from the microcomputer when the TFL flag of the STR register is set to 0 (indicating that TBF is not full).

In master transmission and slave data transmission, the following format is used to load data into TBF from the microcomputer.

[Byte 1]: Number of bytes of transmission data

Between 1 and 256 bytes can be set.

| Number of bytes of transmission data | Data set in byte 1 of TBF |

|--------------------------------------|---------------------------|

| 1                                    | 01H                       |

| 2                                    | 02H                       |

|                                      | i                         |

| 255                                  | FFH                       |

| 256                                  | 00H                       |

#### [Bytes 2 and up]: Transmission data

As much transmission data as is set in byte 1 is set in byte 2 and subsequent bytes.

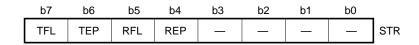

| STR             | Address    | : 0000B (0H) |

|-----------------|------------|--------------|

|                 | Read/write | : Read       |

| Status register | When reset | : 0101××××B  |

STR is a one-byte read register used to indicate the states of TBF and RBF.

# [TFL]

- 1 : TBF is full.